कॅपेसिटरसह इलेक्ट्रिक सर्किट्स

कॅपेसिटरसह इलेक्ट्रिक सर्किट्समध्ये विद्युत उर्जेचे स्त्रोत आणि वैयक्तिक कॅपेसिटर समाविष्ट असतात. कॅपेसिटर म्हणजे डायलेक्ट्रिक लेयरने विभक्त केलेल्या कोणत्याही आकाराच्या दोन कंडक्टरची प्रणाली. कॅपेसिटरच्या क्लॅम्प्सना विद्युत उर्जेच्या स्त्रोताशी स्थिर व्होल्टेज U सह जोडल्यास त्याच्या एका प्लेटवर + Q आणि दुसऱ्यावर -Q जमा होतो.

कॅपेसिटरसह इलेक्ट्रिक सर्किट्समध्ये विद्युत उर्जेचे स्त्रोत आणि वैयक्तिक कॅपेसिटर समाविष्ट असतात. कॅपेसिटर म्हणजे डायलेक्ट्रिक लेयरने विभक्त केलेल्या कोणत्याही आकाराच्या दोन कंडक्टरची प्रणाली. कॅपेसिटरच्या क्लॅम्प्सना विद्युत उर्जेच्या स्त्रोताशी स्थिर व्होल्टेज U सह जोडल्यास त्याच्या एका प्लेटवर + Q आणि दुसऱ्यावर -Q जमा होतो.

या शुल्कांची परिमाण U व्होल्टेजच्या थेट प्रमाणात असते आणि सूत्राद्वारे निर्धारित केली जाते

Q = C ∙ U,

जेथे C हे फॅराड्स (F) मध्ये मोजलेले कॅपेसिटरचे कॅपेसिटन्स आहे.

कॅपेसिटरच्या क्षमतेचे मूल्य त्याच्या एका प्लेटवरील चार्ज आणि त्यांच्यामधील व्होल्टेजच्या गुणोत्तराएवढे आहे, म्हणजे C = Q/U,

कॅपेसिटरची क्षमता प्लेट्सचा आकार, त्यांची परिमाणे, परस्पर मांडणी, तसेच प्लेट्समधील माध्यमाचा डायलेक्ट्रिक स्थिरांक यावर अवलंबून असते.

मायक्रोफारॅड्समध्ये व्यक्त केलेल्या फ्लॅट कॅपेसिटरची कॅपेसिटन्स सूत्राद्वारे निर्धारित केली जाते

C = ((ε0 ∙ εr ∙ S) / d) ∙ 106,

जेथे ε0 हा व्हॅक्यूमचा निरपेक्ष डायलेक्ट्रिक स्थिरांक आहे, εr हा प्लेट्समधील माध्यमाचा सापेक्ष डायलेक्ट्रिक स्थिरांक आहे, S हे प्लेटचे क्षेत्रफळ आहे, m2, d हे प्लेट्समधील अंतर आहे, m.

व्हॅक्यूमचा निरपेक्ष डायलेक्ट्रिक स्थिरांक ε0 = 8.855 ∙ 10-12 F⁄m आहे.

व्होल्टेज U अंतर्गत फ्लॅट कॅपेसिटरच्या प्लेट्समधील इलेक्ट्रिक फील्ड ताकद E चे परिमाण E = U / d या सूत्राद्वारे निर्धारित केले जाते.

इंटरनॅशनल सिस्टम ऑफ युनिट्स (SI) मध्ये, विद्युत क्षेत्राच्या ताकदीचे एकक व्होल्ट प्रति मीटर (V⁄m) आहे.

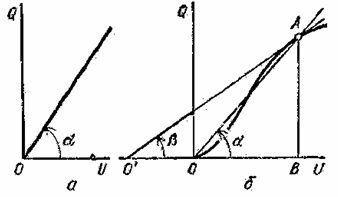

तांदूळ. 1. कॅपेसिटरच्या लटकन-व्होल्टची वैशिष्ट्ये: a — रेखीय, b — नॉन-लिनियर

जर कॅपेसिटरच्या प्लेट्सच्या दरम्यान असलेल्या माध्यमाची सापेक्ष पारगम्यता विद्युत क्षेत्राच्या विशालतेवर अवलंबून नसेल, तर कॅपेसिटरची कॅपेसिटन्स त्याच्या टर्मिनल्सवरील व्होल्टेजच्या विशालतेवर आणि कुलॉम्ब-व्होल्ट वैशिष्ट्यपूर्ण Q वर अवलंबून नसते. = F (U) रेखीय आहे (चित्र 1 , a).

फेरोइलेक्ट्रिक डायलेक्ट्रिक असलेले कॅपेसिटर, ज्यामध्ये सापेक्ष पारगम्यता विद्युत क्षेत्राच्या सामर्थ्यावर अवलंबून असते, त्यांना कुलॉम्ब व्होल्टेजचे नॉनलाइनर वैशिष्ट्य असते (चित्र 1, ब).

अशा नॉन-लीनियर कॅपेसिटर किंवा व्हेरिकॉन्समध्ये, कूलॉम्ब वैशिष्ट्याचा प्रत्येक बिंदू, उदाहरणार्थ बिंदू A, स्थिर कॅपॅसिटन्स Cst = Q / U = (mQ ∙ BA) / (mU ∙ OB) = mC ∙ tan α आणि विभेदक कॅपॅसिटन्स Cdiff = dQ / dU = (mQ ∙ BA) / (mU ∙ O'B) = mC ∙ tanβ, जेथे mC हे अनुक्रमे शुल्क आणि व्होल्टेजसाठी घेतलेल्या mQ आणि mU स्केलवर अवलंबून गुणांक आहे.

प्रत्येक कॅपेसिटर केवळ क्षमतेच्या मूल्याद्वारेच नव्हे तर ऑपरेटिंग व्होल्टेज उरबच्या मूल्याद्वारे देखील दर्शविले जाते, जे घेतले जाते जेणेकरून परिणामी विद्युत क्षेत्राची ताकद डायलेक्ट्रिक ताकदापेक्षा कमी असेल.डायलेक्ट्रिक सामर्थ्य हे व्होल्टेजच्या सर्वात कमी मूल्याद्वारे निर्धारित केले जाते ज्यावर डायलेक्ट्रिकचे विघटन सुरू होते, तसेच त्याचा नाश आणि इन्सुलेट गुणधर्मांचे नुकसान होते.

डायलेक्ट्रिक्स केवळ त्यांच्या विद्युत सामर्थ्यानेच नव्हे तर ρV द्वारे देखील वैशिष्ट्यीकृत आहेत, सुमारे 1010 ते 1020 Ω • सेमी, तर धातूंसाठी ते 10-6 ते 10-4 Ω • पहा.

याव्यतिरिक्त, डायलेक्ट्रिक्ससाठी, विशिष्ट पृष्ठभागावरील प्रतिरोधक ρS ची संकल्पना सादर केली गेली आहे, जी पृष्ठभागाच्या गळती करंटला त्यांचा प्रतिकार दर्शवते. काही डायलेक्ट्रिक्ससाठी, हे मूल्य नगण्य आहे, आणि म्हणून ते खंडित होत नाहीत, परंतु पृष्ठभागावरील इलेक्ट्रिक डिस्चार्जद्वारे अवरोधित केले जातात.

मल्टी-चेन इलेक्ट्रिकल सर्किट्समध्ये समाविष्ट असलेल्या वैयक्तिक कॅपॅसिटरच्या टर्मिनल्सवरील व्होल्टेजच्या विशालतेची गणना करण्यासाठी, समान विद्युत समीकरणे वापरण्याच्या दिलेल्या ईएमएफ स्त्रोतांवर किर्चहॉफच्या कायद्यांची समीकरणे डायरेक्ट करंट सर्किट्ससाठी.

तर, कॅपेसिटरसह मल्टी-चेन इलेक्ट्रिक सर्किटच्या प्रत्येक नोडसाठी, विजेच्या प्रमाणाच्या संवर्धनाचा नियम ∑Q = Q0 न्याय्य आहे, जो एका नोडशी जोडलेल्या कॅपेसिटरच्या प्लेट्सवरील शुल्काची बीजगणितीय बेरीज आहे हे स्थापित करतो. शुल्काच्या बीजगणितीय बेरजेइतके, जे ते एकमेकांशी जोडले जाण्यापूर्वी होते. कॅपेसिटरच्या प्लेट्सवरील प्राथमिक शुल्काच्या अनुपस्थितीत समान समीकरणाचे फॉर्म ∑Q = 0 आहे.

कॅपॅसिटरसह इलेक्ट्रिक सर्किटच्या कोणत्याही सर्किटसाठी, समानता ∑E = ∑Q / C ही सत्य आहे, जी असे सांगते की सर्किटमधील ईएमएफची बीजगणितीय बेरीज कॅपेसिटरच्या टर्मिनल्सवरील व्होल्टेजच्या बीजगणित बेरीजच्या बरोबरीची आहे. या सर्किट मध्ये.

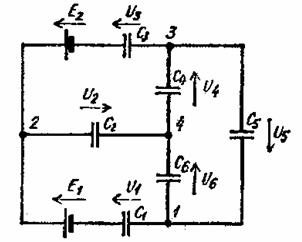

तांदूळ. 2.कॅपेसिटरसह मल्टी-सर्किट इलेक्ट्रिक सर्किट

तर, मल्टी-सर्किट इलेक्ट्रिकल सर्किटमध्ये विद्युत उर्जेचे दोन स्त्रोत आणि प्रारंभिक शून्य शुल्कासह सहा कॅपेसिटर आणि अनियंत्रितपणे निवडलेल्या व्होल्टेजच्या सकारात्मक दिशा U1, U2, U3, U4, U5, U6 (Fig. 2) च्या कायद्यानुसार. तीन स्वतंत्र नोड्स 1, 2, 3 साठी विजेच्या प्रमाणात संवर्धन आपल्याला तीन समीकरणे मिळतात: Q1 + Q6-Q5 = 0, -Q1-Q2-Q3 = 0, Q3-Q4 + Q5 = 0.

तीन स्वतंत्र सर्किट्सची अतिरिक्त समीकरणे 1—2—4—1, 2—3—4—2, 1—4—3—1, त्यांच्या सभोवताल घड्याळाच्या दिशेने असताना, त्यांना E1 = Q1 / C1 + Q2 / C2 -Q6 असे स्वरूप आहे. / C6, -E2 = -Q3 / C3 -Q4 / C4 -Q2 / C2, 0 = Q6 / C6 + Q4 / C4 + Q5 / C5.

सहा रेषीय समीकरणांच्या प्रणालीचे निराकरण आपल्याला प्रत्येक कॅपेसिटर Qi वर शुल्काचे प्रमाण निर्धारित करण्यास आणि Ui = Qi / Ci या सूत्राद्वारे त्याच्या टर्मिनल्स Ui वर व्होल्टेज शोधण्याची परवानगी देते.

ताणतणावांच्या खऱ्या दिशानिर्देश Ui, ज्यांची मूल्ये वजा चिन्हाने प्राप्त केली जातात, समीकरणे तयार केल्यावर मूलतः गृहीत धरलेल्या दिशांच्या विरुद्ध आहेत.

कॅपॅसिटरसह मल्टी-चेन इलेक्ट्रिक सर्किटची गणना करताना, कधीकधी डेल्टामध्ये जोडलेले कॅपेसिटर C12, C23, C31 हे समतुल्य तीन-पॉइंट तारामध्ये जोडलेले कॅपेसिटर C1, C2, C3 सह बदलणे उपयुक्त ठरते.

या प्रकरणात, आवश्यक शक्ती खालीलप्रमाणे आढळतात: C1 = C12 + C31 + (C12 ∙ C31) / C23, C2 = C23 + C12 + (C23 ∙ C12) / C31, C3 = C31 + C23 + (C31 ∙ C23 ) / C12.

रिव्हर्स ट्रान्सफॉर्मेशनमध्ये, सूत्रे वापरा: C12 = (C1 ∙ C2) / (C1 + C2 + C3), C23 = (C2 ∙ C3) / (C1 + C2 + C3), C31 = (C3 ∙ C1) / ( C1 + C2 + C3).

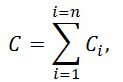

समांतर जोडलेले कॅपेसिटर C1, C2, …, Cn एका कॅपेसिटरने बदलले जाऊ शकतात

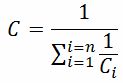

आणि जेव्हा ते मालिकेत जोडलेले असतात - एक कॅपेसिटर ज्याची क्षमता असते

सर्किटमध्ये समाविष्ट असलेल्या कॅपेसिटरमध्ये प्रशंसनीय विद्युत चालकता असलेले डायलेक्ट्रिक्स असल्यास, अशा सर्किटमध्ये लहान प्रवाह दिसतात, ज्याची मूल्ये थेट करंट सर्किट्सची गणना करताना अवलंबलेल्या नेहमीच्या पद्धती आणि प्रत्येकाच्या टर्मिनल्सवरील व्होल्टेजद्वारे निर्धारित केल्या जातात. स्थिर अवस्थेतील कॅपेसिटर सूत्रानुसार आढळतो

Ui = Ri ∙ Ii,

जेथे Ri हा ith कॅपेसिटरच्या डायलेक्ट्रिक थराचा विद्युत प्रतिरोध आहे, Ii हा त्याच कॅपेसिटरचा विद्युत् प्रवाह आहे.

या विषयावर पहा: कॅपेसिटर चार्ज करणे आणि डिस्चार्ज करणे