I2C बस — असाइनमेंट, डिव्हाइस, डेटा ट्रान्सफर, अॅड्रेसिंग

इलेक्ट्रॉनिक सर्किट तयार करताना, बर्याच विकसकांना त्याच्या वैयक्तिक ब्लॉक्सची जुळणी, नमुना आणि संबोधित करण्यासाठी मोठ्या संख्येने इंटरमीडिएट चिप्स वापरण्याची आवश्यकता असते. सहाय्यक चिप्सची संख्या कमी करण्यासाठी, फिलिप्सने 1980 च्या दशकात दोन-वायर द्विदिशात्मक I2C सिरीयल नेटवर्क इंटरफेस प्रस्तावित केला, विशेषत: एकाच उपकरणामध्ये अनेक चिप्स व्यवस्थापित करण्यासाठी डिझाइन केलेले.

आज, एकट्या फिलिप्स इलेक्ट्रॉनिक उपकरणांसाठी विविध उद्देशांसह शंभरहून अधिक I2C-सुसंगत उपकरणे तयार करतात: मेमरी, व्हिडिओ प्रोसेसर सिस्टम, अॅनालॉग-टू-डिजिटल आणि डिजिटल-टू-एनालॉग कन्व्हर्टर, डिस्प्ले ड्रायव्हर्स इ.

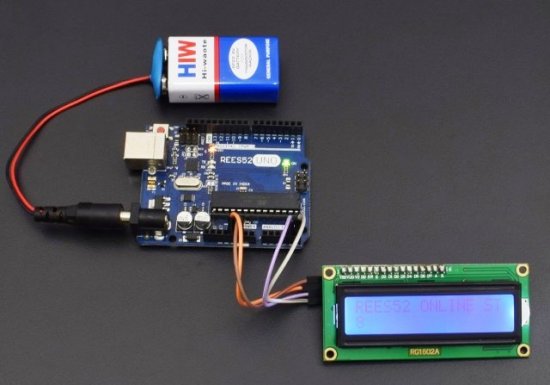

I2C बस ही 100 ते 400 kbps दराने नेहमीच्या "फास्ट" मोडमध्ये सिरीयल 8-बिट डेटा प्रसारित करण्यास सक्षम असलेल्या सिरीयल डेटा एक्सचेंज प्रोटोकॉलमध्ये बदल आहे. डेटा एक्सचेंजची प्रक्रिया येथे फक्त दोन तारांवर लागू केली जाते (सामान्य वायर मोजत नाही): डेटासाठी एसडीए लाइन आणि सिंक्रोनाइझेशनसाठी एससीएल लाइन.

बसला जोडलेल्या उपकरणांच्या आउटपुटच्या कॅस्केडमध्ये खुले कलेक्टर्स किंवा चॅनेल असतात, त्यामुळे AND वायरिंगची प्रतिकृती बनते या वस्तुस्थितीमुळे बस द्वि-दिशात्मक बनते. परिणामी, बस चिप्समधील कनेक्शनची संख्या कमी करते, बोर्डवर कमी आवश्यक पिन आणि ट्रेस सोडते. परिणामी, बोर्ड स्वतःच सोपे, अधिक कॉम्पॅक्ट आणि तांत्रिकदृष्ट्या उत्पादनात अधिक प्रगत असल्याचे दिसून येते.

हा प्रोटोकॉल तुम्हाला अॅड्रेस डीकोडर आणि इतर बाह्य वाटाघाटी लॉजिक अक्षम करण्याची परवानगी देतो. I2C बसवर एकाच वेळी ऑपरेट करू शकणार्या चिप्सची संख्या तिच्या क्षमतेनुसार मर्यादित आहे — कमाल 400 pF.

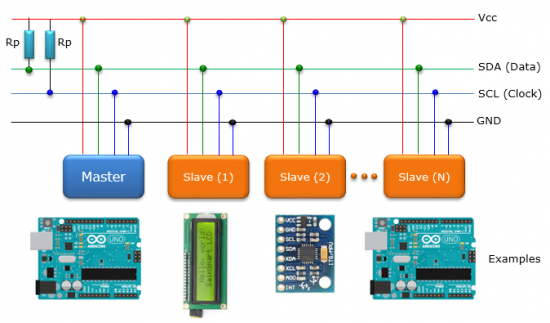

I2C-सुसंगत ICs मध्ये हार्डवेअर नॉइज सप्रेशन अल्गोरिदम आहे जेणेकरुन मजबूत हस्तक्षेपाच्या उपस्थितीतही डेटा अखंडता सुनिश्चित होईल. अशा उपकरणांमध्ये एक इंटरफेस असतो जो पुरवठा व्होल्टेज भिन्न असताना देखील मायक्रोसर्किट्स एकमेकांशी संवाद साधू देतो. खालील आकृतीमध्ये, आपण सामान्य बसद्वारे अनेक मायक्रोक्रिकेट कनेक्ट करण्याच्या तत्त्वासह स्वतःला परिचित करू शकता.

बसशी कनेक्ट केलेल्या प्रत्येक डिव्हाइसचा स्वतःचा अनन्य पत्ता असतो, तो त्याद्वारे निर्धारित केला जातो आणि डिव्हाइसच्या उद्देशानुसार, ते प्राप्तकर्ता किंवा ट्रान्समीटर म्हणून कार्य करू शकते. डेटा प्रसारित करताना, ही उपकरणे मास्टर (मास्टर) किंवा गुलाम (गुलाम) असू शकतात. मास्टर हे असे उपकरण आहे जे डेटा ट्रान्सफर सुरू करते आणि SCL लाइनवर घड्याळ सिग्नल व्युत्पन्न करते. गुलाम, मास्टरच्या संबंधात, गंतव्य साधन आहे.

I2C बसच्या ऑपरेशनच्या कोणत्याही क्षणी, फक्त एक उपकरण मास्टर म्हणून कार्य करू शकते; ते SCL लाईनवर सिग्नल व्युत्पन्न करते.मास्टर एकतर मास्टर रिसीव्हर किंवा मास्टर ट्रान्समीटर असू शकतो.

तत्वतः, बस अनेक भिन्न मास्टर्सना परवानगी देते, परंतु नियंत्रण सिग्नल तयार करण्याच्या आणि बसच्या स्थितीचे परीक्षण करण्याच्या वैशिष्ट्यांवर निर्बंध लादते; याचा अर्थ असा की अनेक मास्टर्स एकाच वेळी प्रसारित करणे सुरू करू शकतात, परंतु लवादामुळे या प्रकारचे विरोधाभास दूर केले जातात, म्हणजेच बस दुसर्या मास्टरने व्यापलेली असल्याचे समजल्यावर मास्टर ज्या प्रकारे वागतो.

उपकरणांच्या जोडीचे सिंक्रोनाइझेशन सुनिश्चित केले जाते की सर्व उपकरणे बसशी जोडलेली आहेत, "AND" वायरिंग तयार करतात. सुरुवातीला, SDA आणि SCL सिग्नल जास्त आहेत.

सुरू करा आणि थांबा

एक्स्चेंज मास्टरने «START» स्थिती निर्माण करून सुरू होते: SDA लाईनवर, सिग्नल उच्च ते निम्न स्थितीकडे जातो, तर SCL लाइनमध्ये स्थिर उच्च पातळी असते. बसशी जोडलेली सर्व उपकरणे ही परिस्थिती एक्स्चेंज सुरू करण्याची आज्ञा मानतात.

बसमधील डेटा प्रसारित करताना प्रत्येक मास्टर SCL लाईनवर एक स्वतंत्र घड्याळ सिग्नल तयार करतो.

एक्सचेंज मास्टरद्वारे STOP स्थितीच्या निर्मितीसह समाप्त होते: SDA लाईनवर सिग्नल कमी ते उच्च पर्यंत बदलतो, तर SCL लाइनमध्ये स्थिर उच्च पातळी असते.

ड्रायव्हर नेहमी START आणि STOP सिग्नलचा स्रोत म्हणून काम करतो. "START" सिग्नल निश्चित होताच, याचा अर्थ ओळ व्यस्त आहे. जेव्हा STOP सिग्नल आढळतो तेव्हा लाइन विनामूल्य असते.

START स्थिती घोषित केल्यानंतर लगेच, मास्टर SCL लाईन खाली स्विच करतो आणि पहिल्या मेसेज बाइटचा सर्वात महत्वाचा भाग SDA लाईनला पाठवतो. संदेशातील बाइट्सची संख्या मर्यादित नाही.SDA लाईनवरील बदल केवळ SCL लाईनवरील सिग्नल पातळी कमी असताना सक्षम केले जातात. डेटा वैध आहे आणि जेव्हा सिंक पल्स जास्त असेल तेव्हाच बदलू नये.

स्लेव्ह रिसीव्हरकडून मास्टर ट्रान्समीटरकडून बाइट मिळाल्याची पोचपावती आठवा डेटा बिट प्राप्त झाल्यानंतर एसडीए लाइनवर एक विशेष पावती बिट सेट करून केली जाते.

पुष्टी

तर, ट्रान्समीटरवरून रिसीव्हरला 8 बिट डेटा पाठवल्याने SDA लाईनवर रिसीव्हिंग डिव्हाईस कमी होते तेव्हा SCL लाईनवर अतिरिक्त पल्स होते, हे दर्शवते की त्याला संपूर्ण बाइट प्राप्त झाला आहे.

पुष्टीकरण हा डेटा ट्रान्सफर प्रक्रियेचा अविभाज्य भाग आहे. मास्टर सिंक पल्स व्युत्पन्न करतो. पावती घड्याळ सक्रिय असताना ट्रान्समीटर SDA ला निम्न स्थिती पाठवतो. सिंक पल्स उच्च असताना, प्राप्तकर्त्याने SDA कमी ठेवणे आवश्यक आहे.

जर डेस्टिनेशन स्लेव्हने त्याचा पत्ता मान्य केला नाही, उदाहरणार्थ तो सध्या व्यस्त असल्यामुळे, डेटा लाइन उच्च ठेवली पाहिजे. मास्टर नंतर डिस्पॅच रद्द करण्यासाठी STOP सिग्नल देऊ शकतो.

जर रिसेप्शन मास्टर रिसीव्हरद्वारे केले जाते, तर ट्रान्समिशन पूर्ण झाल्यानंतर स्लेव्ह ट्रान्समीटरला सूचित करणे बंधनकारक आहे - शेवटच्या बाइटची पुष्टी करून नाही. स्लेव्ह ट्रान्समीटर डेटा लाइन रिलीज करतो जेणेकरून मास्टर STOP सिग्नल किंवा पुनरावृत्ती होणारा START सिग्नल जारी करू शकेल.

डिव्हाइसेसचे सिंक्रोनाइझेशन हे सुनिश्चित केले जाते की SCL लाइनचे कनेक्शन "AND" तत्त्वानुसार केले जातात.

SCL लाईनचे निम्न ते उच्च पर्यंतचे संक्रमण नियंत्रित करण्याचा एकमेव अधिकार मास्टरकडे नाही.स्लेव्हला प्राप्त झालेल्या बिटवर प्रक्रिया करण्यासाठी अधिक वेळ लागल्यास, तो पुढील बिट डेटा प्राप्त करण्यास तयार होईपर्यंत स्वतंत्रपणे SCL कमी ठेवू शकतो. अशा परिस्थितीत एससीएल लाइन सर्वात प्रदीर्घ लो-लेव्हल सिंक पल्सच्या कालावधीसाठी कमी असेल.

दीर्घ कालावधी संपेपर्यंत सर्वात कमी शाश्वत कमी असलेली उपकरणे निष्क्रिय राहतील. सर्व उपकरणांनी कमी समक्रमण कालावधी पूर्ण केल्यावर, SCL उच्च पातळीवर जाईल.

सर्व उपकरणे उच्च घड्याळ सुरू करतील आणि त्याचा कालावधी पूर्ण करणारे पहिले उपकरण SCL लाईन कमी सेट करणारे पहिले असेल. परिणामी, SCL च्या निम्न स्थितीचा कालावधी एका उपकरणाच्या सिंक्रोनाइझेशन पल्सच्या प्रदीर्घ निम्न अवस्थेद्वारे निर्धारित केला जाईल आणि उच्च स्थितीचा कालावधी त्यापैकी एकाच्या सिंक्रोनाइझेशनच्या सर्वात कमी कालावधीद्वारे निर्धारित केला जाईल. उपकरणे

बिट आणि बाइट स्तरावर डेटा ट्रान्समिशन नियंत्रित करण्यासाठी रिसीव्हर्सद्वारे सिंक्रोनाइझेशन सिग्नलचा वापर केला जाऊ शकतो.

डिव्हाइस उच्च दराने बाइट्स प्राप्त करण्यास सक्षम असल्यास, परंतु प्राप्त बाइट संचयित करण्यासाठी किंवा पुढील बाइट प्राप्त करण्यासाठी तयार होण्यासाठी विशिष्ट वेळ घेत असल्यास, बाइट प्राप्त केल्यानंतर आणि ते स्वीकारल्यानंतर ते SCL कमी ठेवू शकते, सक्तीने ट्रान्समीटर स्टँडबाय स्थितीत.

बिल्ट-इन हार्डवेअर सर्किट नसलेला मायक्रोकंट्रोलर, उदाहरणार्थ बिट स्तरावर, त्यांच्या निम्न स्थितीचा कालावधी वाढवून घड्याळाचा वेग कमी करू शकतो. परिणामी, मास्टर डिव्हाइसचा बॉड रेट त्याच्या गतीने निर्धारित केला जाईल. धीमे डिव्हाइस.

संबोधित करत आहे

I2C बसशी जोडलेल्या प्रत्येक यंत्रास एक अद्वितीय प्रोग्राम पत्ता असतो ज्यावर मास्टर विशिष्ट कमांड पाठवून त्यास संबोधित करतो. समान प्रकारचे मायक्रोसर्किट्स अॅड्रेस सिलेक्टरद्वारे दर्शविले जातात, एकतर सिलेक्टरच्या डिजिटल इनपुटच्या स्वरूपात किंवा अॅनालॉग स्वरूपात लागू केले जातात. बसला जोडलेल्या उपकरणांच्या पत्त्याच्या जागेत पत्ते विभागले जातात.

सामान्य मोड सात-बिट अॅड्रेसिंग गृहीत धरतो. अॅड्रेसिंग खालीलप्रमाणे कार्य करते: «START» कमांडनंतर, मास्टर पहिला बाइट पाठवतो, जो मास्टरशी संवाद साधण्यासाठी कोणत्या स्लेव्ह डिव्हाइसची आवश्यकता आहे हे निर्धारित करतो. एक सामान्य कॉल पत्ता देखील आहे जो बसमधील सर्व उपकरणे परिभाषित करतो, सर्व उपकरणे (सैद्धांतिकदृष्ट्या) त्यास पावतीसह प्रतिसाद देतात, परंतु व्यवहारात हे दुर्मिळ आहे.

तर पहिल्या बाइटचे पहिले सात बिट्स हे स्लेव्ह अॅड्रेस आहेत. सर्वात कमी महत्त्वाचा बिट, आठवा, डेटा पाठविण्याची दिशा दर्शवितो. जर तेथे «0» असेल, तर माहिती मालकाकडून या गुलामाकडे लिहिली जाईल. जर «1», माहिती या गुलामाकडून मास्टरद्वारे वाचली जाईल.

मास्टरने अॅड्रेस बाइट पाठवणे पूर्ण केल्यानंतर, प्रत्येक स्लेव्ह त्याच्या पत्त्याची त्याच्याशी तुलना करतो. समान पत्ता असलेला कोणीही गुलाम आहे आणि अॅड्रेस बाइटच्या किमान महत्त्वपूर्ण बिटच्या मूल्यावर अवलंबून, स्लेव्ह ट्रान्समीटर किंवा स्लेव्ह रिसीव्हर म्हणून परिभाषित केले आहे.

गुलाम पत्त्यामध्ये निश्चित आणि प्रोग्राम करण्यायोग्य भाग समाविष्ट असू शकतात. बर्याचदा एकाच प्रकारच्या डिव्हाइसेसची एक मोठी संख्या एकाच सिस्टममध्ये कार्य करते, नंतर पत्त्याचा प्रोग्राम करण्यायोग्य भाग बसमध्ये जास्तीत जास्त समान प्रकारच्या डिव्हाइसेसचा वापर करण्यास अनुमती देतो. अॅड्रेस बाइटमधील किती बिट्स प्रोग्राम करण्यायोग्य आहेत हे चिपवरील फ्री पिनच्या संख्येवर अवलंबून असते.

काहीवेळा प्रोग्रामेबल अॅड्रेस रेंजच्या अॅनालॉग सेटिंगसह एक पिन पुरेसा असतो, उदाहरणार्थ SAA1064 - एक LED इंडिकेटर ड्रायव्हर ज्यामध्ये अशी अंमलबजावणी आहे. विशिष्ट पिनची संभाव्यता चिपच्या अॅड्रेस स्पेसचा ऑफसेट निर्धारित करते जेणेकरून त्याच प्रकारच्या चिप्स एकाच बसमध्ये कार्यरत नसतात. I2C बसला सपोर्ट करणार्या सर्व चिप्समध्ये निर्मात्याने दस्तऐवजीकरणात निर्दिष्ट केलेल्या पत्त्यांचा संच असतो.

संयोजन «11110XX» 10-बिट अॅड्रेसिंगसाठी राखीव आहे. जर आपण "START" कमांडपासून "STOP" कमांडमध्ये डेटाच्या देवाणघेवाणीची कल्पना केली तर ते असे दिसेल:

साधे आणि एकत्रित डेटा एक्सचेंज फॉरमॅटला येथे अनुमती आहे. एकत्रित स्वरूपाचा अर्थ असा की "START" आणि "STOP" दरम्यान मास्टर आणि स्लेव्ह रिसीव्हर आणि ट्रान्समीटर म्हणून काम करू शकतात, हे अनुक्रमांक मेमरी व्यवस्थापनासाठी उपयुक्त आहे.

डेटाच्या पहिल्या बाइटला मेमरी अॅड्रेस ट्रान्सफर करू द्या. नंतर, «START» कमांडची पुनरावृत्ती करून आणि स्लेव्ह पत्ता वाचून, मेमरी डेटा कार्य करेल. पूर्वी ऍक्सेस केलेला पत्ता स्वयंचलितपणे वाढवण्याचे किंवा कमी करण्याचे निर्णय डिव्हाइस डेव्हलपरने चिप दस्तऐवजाचा आधी अभ्यास केल्यानंतर घेतले आहेत. एक मार्ग किंवा दुसरा, START कमांड प्राप्त केल्यानंतर, सर्व उपकरणांनी त्यांचे तर्क पुनर्संचयित केले पाहिजे आणि पत्त्याला आता नाव दिले जाईल या वस्तुस्थितीसाठी तयार केले पाहिजे.