ट्रान्सफॉर्मर विंडिंग्समध्ये ओव्हरव्होल्टेज

ट्रान्सफॉर्मर इन्सुलेशनचे आकारमान आणि डिझाइन निवडणे ऑपरेशन दरम्यान ट्रान्सफॉर्मर इन्सुलेशनच्या विविध भागांवर काम करणारे ताण आणि ट्रान्सफॉर्मरचे विश्वसनीय ऑपरेशन सुनिश्चित करण्यासाठी डिझाइन केलेले चाचणी निर्धारित केल्याशिवाय अशक्य आहे.

ट्रान्सफॉर्मर इन्सुलेशनचे आकारमान आणि डिझाइन निवडणे ऑपरेशन दरम्यान ट्रान्सफॉर्मर इन्सुलेशनच्या विविध भागांवर काम करणारे ताण आणि ट्रान्सफॉर्मरचे विश्वसनीय ऑपरेशन सुनिश्चित करण्यासाठी डिझाइन केलेले चाचणी निर्धारित केल्याशिवाय अशक्य आहे.

या प्रकरणात, जेव्हा विजेच्या लाटेच्या लाटा त्याच्या इनपुटवर आदळतात तेव्हा ट्रान्सफॉर्मर इन्सुलेशनवर कार्य करणारे व्होल्टेज बहुतेक वेळा निर्णायक असतात. हे व्होल्टेज, ज्यांना आवेग व्होल्टेज देखील म्हणतात, जवळजवळ सर्व प्रकरणांमध्ये अनुदैर्ध्य वळण इन्सुलेशनची निवड निर्धारित करतात आणि बर्याच बाबतीत मुख्य वळण इन्सुलेशन, स्विचिंग डिव्हाइस इन्सुलेशन इ.

ओव्हरव्होल्टेजच्या निर्धारामध्ये संगणक तंत्रज्ञानाचा वापर केल्याने विंडिंग्समधील आवेग प्रक्रियेच्या गुणात्मक विचारापासून ओव्हरव्होल्टेजच्या थेट गणनेकडे आणि त्यांच्या परिणामांचा डिझाईन प्रॅक्टिसमध्ये परिचय करण्यास अनुमती मिळते.

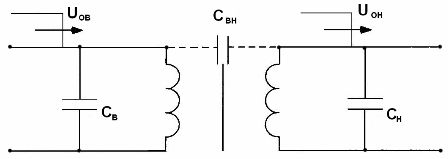

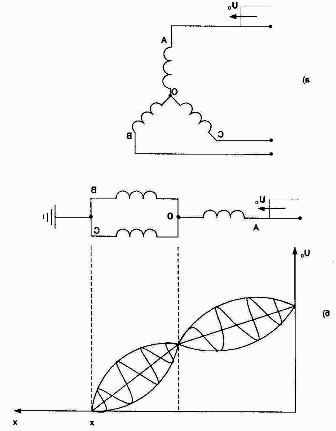

ओव्हरव्होल्टेजची गणना करण्यासाठी, ट्रान्सफॉर्मरचे विंडिंग समतुल्य सर्किटद्वारे दर्शविले जाते जे विंडिंगच्या घटकांमधील प्रेरक आणि कॅपेसिटिव्ह कनेक्शनचे पुनरुत्पादन करते (आकृती 1).सर्व समतुल्य सर्किट्स वळण आणि विंडिंगमधील कॅपेसिटन्सचा विचार करतात.

आकृती 1. ट्रान्सफॉर्मरचे समतुल्य सर्किट: UOV — उच्च व्होल्टेज विंडिंगमधील घटना लहर, UOH — कमी व्होल्टेज विंडिंगमधील घटना लहर, SV आणि CH — अनुक्रमे उच्च आणि कमी व्होल्टेज विंडिंग्सच्या वळणांमधील कॅपेसिटन्स, SVN — कॅपेसिटन्स दरम्यान उच्च आणि कमी व्होल्टेज सह windings.

ट्रान्सफॉर्मरमध्ये लहरी प्रक्रिया

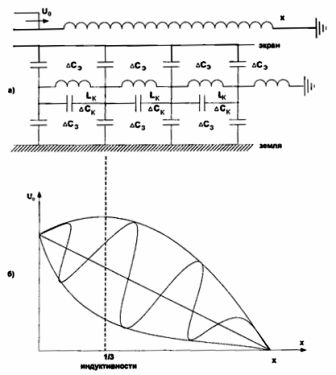

इंटरटर्न कॅपेसिटन्स, स्क्रीन आणि इंडक्टन्समधील कॅपेसिटन्स आणि इंडक्टन्स आणि ग्राउंड (आकृती 2a) यांच्यातील कॅपेसिटन्स लक्षात घेऊन ट्रान्सफॉर्मरला एक प्रेरक घटक मानले जाईल.

ओव्हरव्होल्टेजची गणना करण्यासाठी खालील सूत्रे वापरली जातात:

जेथे: t म्हणजे ट्रान्सफॉर्मरवर लाट आल्यानंतरची वेळ, T हा ओव्हरव्होल्टेज टाइम कॉन्स्टंट आहे, ZEKV हा समतुल्य सर्किट रेझिस्टन्स आहे, Z2 हा लाइन रेझिस्टन्स आहे, Uo हा सुरुवातीच्या वेळी ओव्हरव्होल्टेज आहे

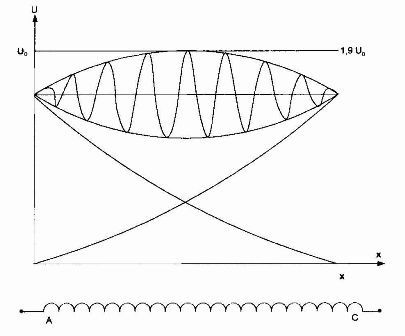

आकृती 2. ग्राउंडेड न्यूट्रलसह ट्रान्सफॉर्मरच्या वळणाच्या बाजूने व्होल्टेज वेव्हचा प्रसार: अ) योजनाबद्ध आकृती, ब) ग्राउंड टर्मिनलसह सिंगल-फेज ट्रान्सफॉर्मरसाठी वळणाच्या लांबीवर व्होल्टेज वेव्हचे अवलंबन: Uo — ड्रॉप व्होल्टेज वेव्ह, ∆Ce — कॉइल आणि स्क्रीनमधील कॅपॅसिटन्स, ∆Ck — वळणांमधील अंतर्निहित कॅपेसिटन्स, ∆С3 — कॉइल आणि ग्राउंडमधील कॅपॅसिटन्स, ∆Lк — कॉइल लेयर्सचे इंडक्टन्स.

समतुल्य सर्किटमध्ये इंडक्टन्स आणि कॅपेसिटन्स दोन्ही असल्याने, एक दोलन एलसी सर्किट उद्भवते (व्होल्टेज चढउतार आकृती 2b मध्ये दर्शविलेले आहेत).

दोलनांचे मोठेपणा घटना लहरीच्या मोठेपणाच्या 1.3 - 1.4 आहे, म्हणजे.Uppep = (1.3-1.4) Uo, आणि ओव्हरव्होल्टेजचे सर्वात मोठे मूल्य वळणाच्या पहिल्या तृतीयांशाच्या शेवटी येईल, म्हणून, ट्रान्सफॉर्मरच्या बांधकामात, 1/3 वार्याने उर्वरीत इन्सुलेशनच्या तुलनेत मजबुतीकरण केले आहे. .

ओव्हरव्होल्टेज टाळण्यासाठी, जमिनीच्या संदर्भात कॅपेसिटरच्या चार्जिंग करंटची भरपाई करणे आवश्यक आहे. या उद्देशासाठी, सर्किटमध्ये अतिरिक्त स्क्रीन (ढाल) स्थापित केली आहे. स्क्रीन वापरताना, स्क्रीनवरील विंडिंग्सची कॅपेसिटन्स पृथ्वीच्या वळणाच्या कॅपेसिटन्सच्या समान असेल, म्हणजे. ∆CE = ∆C3.

व्होल्टेज वर्ग UH = 110 kV आणि उच्च असलेल्या ट्रान्सफॉर्मरमध्ये शिल्डिंग केले जाते. ढाल सहसा ट्रान्सफॉर्मर केसिंग जवळ स्थापित केले जाते.

पृथक तटस्थ सह सिंगल-फेज ट्रान्सफॉर्मर

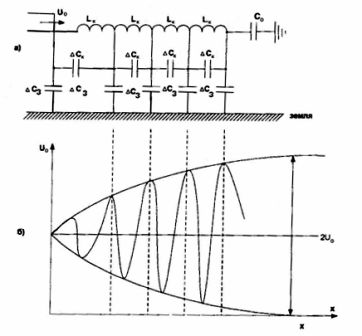

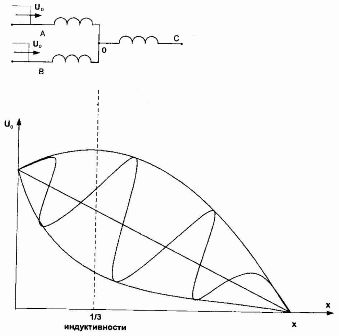

पृथक् तटस्थ उपस्थितीचा अर्थ असा आहे की पृथ्वी आणि वळण यांच्यामध्ये कॅपेसिटन्स Co आहे, म्हणजेच पृथ्वी टर्मिनल ट्रान्सफॉर्मरच्या समतुल्य सर्किटमध्ये कॅपेसिटन्स जोडला जातो, परंतु स्क्रीन काढून टाकली जाते (आकृती 3a).

आकृती 3. वेगळ्या तटस्थ असलेल्या ट्रान्सफॉर्मरच्या वळणावर व्होल्टेज वेव्हचा प्रसार: अ) समतुल्य ट्रान्सफॉर्मरचा योजनाबद्ध आकृती, ब) विंडिंगच्या लांबीवर घटना वेव्ह व्होल्टेजचे अवलंबन.

या समतुल्य सर्किटसह एक दोलन सर्किट देखील तयार होते. तथापि, कॅपॅसिटन्स Co मुळे, इंडक्टन्स आणि कॅपॅसिटन्सच्या सीरिज कनेक्शनसह एक दोलन एलसी सर्किट आहे. या प्रकरणात, महत्त्वपूर्ण कॅपेसिटन्स सह सह, विंडिंगच्या शेवटी सर्वोच्च व्होल्टेज दिसून येईल (ओव्हरव्होल्टेज 2Uo पर्यंतच्या मूल्यांपर्यंत पोहोचू शकते). कॉइलमध्ये व्होल्टेज बदलाचे स्वरूप आकृती 3b मध्ये दर्शविले आहे.

पृथक तटस्थ असलेल्या ट्रान्सफॉर्मरच्या विंडिंगमध्ये ओव्हरव्होल्टेज दोलनांचे मोठेपणा कमी करण्यासाठी, जमिनीच्या संदर्भात आउटपुट C ची क्षमता कमी करणे किंवा कॉइलची स्व-क्षमता वाढवणे आवश्यक आहे. नंतरची पद्धत सहसा वापरली जाते. हाय-व्होल्टेज वाइंडिंगच्या कॉइलमधील स्व-कॅपॅसिटन्स ∆Ck वाढवण्यासाठी, सर्किटमध्ये विशेष कॅपेसिटर प्लेट्स (रिंग्ज) समाविष्ट केल्या जातात.

थ्री-फेज ट्रान्सफॉर्मरमध्ये वेव्ह प्रक्रिया

थ्री-फेज ट्रान्सफॉर्मरमध्ये, विंडिंगच्या बाजूने घटना लहरी प्रसार प्रक्रियेचे स्वरूप आणि ओव्हरव्होल्टेजची तीव्रता यावर प्रभाव पडतो:

अ) कॉइल कनेक्शन आकृती,

b) लाट लाट ज्या टप्प्यात येते त्यांची संख्या.

उच्च-व्होल्टेज विंडिंगसह तीन-फेज ट्रान्सफॉर्मर, तारा ठोसपणे ग्राउंडेड न्यूट्रलसह जोडलेला आहे

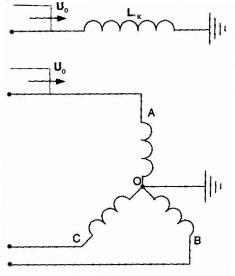

ट्रान्सफॉर्मरच्या एका टप्प्यात घटना लाट लाट येऊ द्या (आकृती 4).

या प्रकरणात विंडिंग्सच्या बाजूने ओव्हरव्होल्टेज लहरींच्या प्रसाराची प्रक्रिया ग्राउंडेड न्यूट्रलसह सिंगल-फेज ट्रान्सफॉर्मरमधील प्रक्रियांसारखीच असेल (प्रत्येक टप्प्यात सर्वाधिक व्होल्टेज वळणाच्या 1/3 मध्ये असेल), तर ते लाट लाटेपर्यंत किती टप्पे पोहोचतात यावर अवलंबून नाहीत. या. कॉइलच्या या भागातील ओव्हरव्होल्टेजचे मूल्य Upep = (1.3-1.4) Uo च्या बरोबरीचे आहे.

आकृती 4. तीन-फेज ट्रान्सफॉर्मरचे समतुल्य सर्किट उच्च-व्होल्टेज विंडिंगसह तटस्थ अर्थ नेटवर्कसह ताराशी जोडलेले आहे. लाट लाट एका टप्प्यात येते.

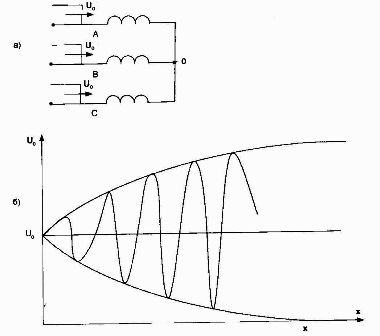

पृथक तटस्थ सह थ्री-फेज तारा-कनेक्ट केलेले उच्च-व्होल्टेज ट्रान्सफॉर्मर

लाट लाट एका टप्प्यात येऊ द्या.ट्रान्सफॉर्मरचे समतुल्य सर्किट, तसेच ट्रान्सफॉर्मर विंडिंगमध्ये घटना लहरींचा प्रसार, आकृती 5 मध्ये दर्शविला आहे.

आकृती 5. तारा-कनेक्ट केलेल्या उच्च-व्होल्टेज विंडिंगसह तीन-फेज ट्रान्सफॉर्मरचे समतुल्य सर्किट (a) आणि जेव्हा लाट एका टप्प्यात येते (b) केससाठी अवलंबित्व U = f (x).

या प्रकरणात, दोन स्वतंत्र दोलन झोन दिसतात. फेज A मध्ये एक दोलन श्रेणी असेल आणि ज्या परिस्थितीत ते उद्भवतात, आणि टप्प्याटप्प्याने B आणि C मध्ये आणखी एक दोलन लूप असेल, दोन्ही प्रकरणांमध्ये दोलन श्रेणी देखील भिन्न असेल. सर्वात मोठी ओव्हरव्होल्टेज घटना लाट लाट प्राप्त वळण वर असेल. शून्य बिंदूवर, 2/3 Uo पर्यंत ओव्हरव्होल्टेज शक्य आहेत (या क्षणी सामान्य मोडमध्ये U = 0, म्हणून, ऑपरेटिंग व्होल्टेज Uoperation च्या संदर्भात ओव्हरव्होल्टेज सर्वात धोकादायक आहेत, कारण U0 >> Uoperation).

सर्ज वेव्हला A आणि B या दोन टप्प्यांतून जाऊ द्या. ट्रान्सफॉर्मरचे समतुल्य सर्किट तसेच ट्रान्सफॉर्मर विंडिंगमधील घटना लहरी प्रसार आकृती 6 मध्ये दर्शविला आहे.

आकृती 6. तारा-कनेक्ट केलेल्या उच्च-व्होल्टेज विंडिंगसह तीन-फेज ट्रान्सफॉर्मरचे समतुल्य सर्किट आणि जेव्हा लहर दोन टप्प्यांत येते तेव्हा केससाठी अवलंबित्व U = f (x).

ज्या टप्प्यांपर्यंत लाट येते त्या टप्प्यांच्या विंडिंगमध्ये व्होल्टेज (1.3 — 1.4) Uo असेल. तटस्थ व्होल्टेज 4/3 Uo आहे. या प्रकरणात ओव्हरव्होल्टेजपासून संरक्षण करण्यासाठी, एक अटककर्ता ट्रान्सफॉर्मरच्या तटस्थशी जोडलेला आहे.

सर्ज वेव्ह तीन टप्प्यांत येऊ द्या. ट्रान्सफॉर्मरचे समतुल्य सर्किट तसेच ट्रान्सफॉर्मर विंडिंगमधील घटना लहरींचा प्रसार आकृती 7 मध्ये दर्शविला आहे.

आकृती 7.तारा-कनेक्ट केलेल्या उच्च-व्होल्टेज विंडिंगसह तीन-फेज ट्रान्सफॉर्मरचे समतुल्य सर्किट (a) आणि जेव्हा लहर तीन टप्प्यांत येते तेव्हा केससाठी अवलंबित्व U = f (x).

थ्री-फेज ट्रान्सफॉर्मरच्या प्रत्येक टप्प्यात ओव्हरव्होल्टेज ड्रॉप वेव्हच्या प्रसार प्रक्रिया वेगळ्या आउटपुटसह सिंगल-फेज ट्रान्सफॉर्मरमधील प्रक्रियांसारख्याच असतील. या मोडमधील सर्वोच्च व्होल्टेज तटस्थ असेल आणि 2U0 असेल. ट्रान्सफॉर्मर ओव्हरव्होल्टेजचे हे प्रकरण सर्वात गंभीर आहे.

थ्री-फेज हाय-व्होल्टेज डेल्टा-जखमे ट्रान्सफॉर्मर

डेल्टामध्ये जोडलेल्या तीन-फेज हाय-व्होल्टेज ट्रान्सफॉर्मरच्या एका फेज A मधून लाट लाट जाऊ द्या, इतर दोन टप्पे (B आणि C) ग्राउंडेड मानले जातात (आकृती 8).

आकृती 8. डेल्टा (ए) मध्ये जोडलेल्या उच्च-व्होल्टेज विंडिंगसह तीन-फेज ट्रान्सफॉर्मरचे समतुल्य सर्किट आणि जेव्हा लहर एका टप्प्यात येते तेव्हा केससाठी अवलंबन U = f (x).

विंडिंग्स AC आणि BC एक ओव्हरव्होल्टेज (1.3 - 1.4) Uo च्या संपर्कात येतील. हे ओव्हरव्होल्टेज ट्रान्सफॉर्मरच्या ऑपरेशनसाठी धोकादायक नाहीत.

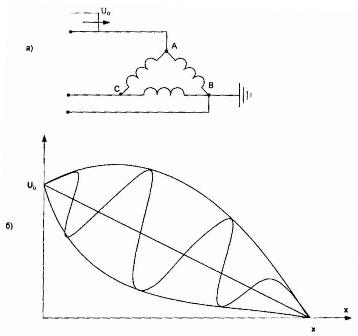

ओव्हरव्होल्टेज लहरी दोन टप्प्यांत येऊ द्या (A आणि B), स्पष्टीकरणात्मक आलेख आकृती 9 मध्ये दाखवले आहेत. या मोडमध्ये, AB आणि BC या विंडिंग्जमधील ओव्हरव्होल्टेज लहरींचा प्रसार a च्या संबंधित विंडिंग्जमधील प्रक्रियांसारखा असेल. थ्री-फेज ग्राउंड ट्रान्सफॉर्मर टर्मिनल. या. या विंडिंगमध्ये ओव्हरव्होल्टेज व्हॅल्यू (1.3 — 1.4) Uo असेल आणि AC वाइंडिंगमध्ये ते व्हॅल्यू (1.8 — 1.9) Uo पर्यंत पोहोचेल.

आकृती 9. अवलंबित्व U = f (x) केससाठी जेव्हा ओव्हरव्होल्टेज लहर डेल्टामध्ये जोडलेल्या उच्च-व्होल्टेज वळण असलेल्या तीन-फेज ट्रान्सफॉर्मरच्या दोन टप्प्यांतून जाते.

हाय-व्होल्टेज डेल्टा-कनेक्टेड वळण असलेल्या थ्री-फेज ट्रान्सफॉर्मरच्या सर्व तीन टप्प्यांमधून लाट लाटा जाऊ द्या.

या मोडमधील सर्व टप्प्यांचे विंडिंग ओव्हरव्होल्टेज (1.8 - 1.9) Uo च्या संपर्कात येतील. जर दोन किंवा तीन तारांमधून एकाच वेळी लाटाची लाट आली, तर वळणाच्या मध्यभागी, ज्यामध्ये दोन्ही बाजूंनी लाटा येतात, ट्रान्सफॉर्मरच्या ऑपरेशनसाठी धोकादायक असलेल्या मोठेपणासह व्होल्टेज चढउतार होऊ शकतात.

ट्रान्सफॉर्मर लाट संरक्षण

विंडिंग्सच्या मुख्य इन्सुलेशनचे सर्वात धोकादायक ओव्हरव्होल्टेज तीन तारांद्वारे डेल्टा कनेक्शन (विंडिंगच्या मध्यभागी) किंवा पृथक तटस्थ (जवळजवळ तटस्थ) तारा असलेल्या ट्रान्सफॉर्मरमध्ये एकाच वेळी लाटा येण्याच्या बाबतीत उद्भवू शकतात. . या प्रकरणात, परिणामी ओव्हरव्होल्टेजचे मोठेपणा आउटपुटच्या व्होल्टेजच्या दुप्पट किंवा इनपुट वेव्हच्या चारपट मोठेपणाकडे जातात. ट्रान्सफॉर्मरच्या विंडिंग्सच्या कनेक्शन योजनेची पर्वा न करता, ट्रान्सफॉर्मरवर समोरच्या बाजूची लाट आल्यावर सर्व प्रकरणांमध्ये धोकादायक टर्न-टू-टर्न इन्सुलेशन ओव्हरव्होल्टेज होऊ शकतात.

अशाप्रकारे, ओव्हरव्होल्टेज आणि विंडिंगसह त्यांचे वितरण झाल्यास सर्व ट्रान्सफॉर्मर्ससाठी, त्यांच्या विशालतेचा अंदाज घेण्यासाठी, ट्रान्सफॉर्मर्सच्या समतुल्य सर्किट्समधील कॅपेसिटन्स (आणि केवळ इंडक्टन्सच नाही) विचारात घेणे आवश्यक आहे. प्राप्त केलेल्या ओव्हरव्होल्टेज मूल्यांची अचूकता मुख्यत्वे कॅपेसिटन्स मापनाच्या अचूकतेवर अवलंबून असते.

ट्रान्सफॉर्मरच्या डिझाइनमध्ये ओव्हरव्होल्टेज टाळण्यासाठी, हे प्रदान केले आहे:

-

एक अतिरिक्त स्क्रीन जी चार्जिंग करंट वितरीत करते, म्हणून, ओव्हरव्होल्टेज कमी केले जातात.तसेच, ट्रान्सफॉर्मर वळणावर स्क्रीन काही विशिष्ट बिंदूंवर फील्ड स्ट्रेंथ कमी करते,

-

त्याच्या काही भागांमध्ये विंडिंग्सचे इन्सुलेशन मजबूत करणे (ट्रान्सफॉर्मरच्या विंडिंग्जची रचनात्मक बदली),

-

ट्रान्सफॉर्मरच्या समोर आणि त्याच्या नंतर - बाह्य आणि अंतर्गत ओव्हरव्होल्टेजच्या विरूद्ध, तसेच ट्रान्सफॉर्मरच्या तटस्थमध्ये एक अटकर स्थापित करणे.