अॅनालॉग-टू-डिजिटल कनवर्टर - उद्देश, वर्गीकरण आणि ऑपरेशनचे सिद्धांत

अॅनालॉग-टू-डिजिटल कन्व्हर्टर (ADC) नावाचे इलेक्ट्रॉनिक उपकरण अॅनालॉग सिग्नलला डिजिटल सिग्नलमध्ये रूपांतरित करण्यासाठी वापरले जाते (वाचण्यायोग्य बायनरी कोड प्रकार क्रमात). अॅनालॉग सिग्नलला डिजिटलमध्ये रूपांतरित करण्याच्या प्रक्रियेत, खालील गोष्टी लागू केल्या जातात: सॅम्पलिंग, क्वांटायझेशन आणि कोडिंग.

विशिष्ट कालांतराने आणि घड्याळाच्या सिग्नलच्या कालावधीशी संबंधित असलेल्या वैयक्तिक (अविभक्त) मूल्यांच्या वेळ-सतत अॅनालॉग सिग्नलमधून नमुने घेणे असे सॅम्पलिंग समजले जाते.

क्वांटायझेशनमध्ये सॅम्पलिंग दरम्यान निवडलेल्या अॅनालॉग सिग्नलचे मूल्य जवळच्या क्वांटायझेशन स्तरावर गोलाकार करणे समाविष्ट असते आणि क्वांटायझेशन स्तरांची स्वतःची अनुक्रम संख्या असते आणि हे स्तर एका निश्चित डेल्टा मूल्याद्वारे एकमेकांपासून भिन्न असतात, जे क्वांटायझेशन चरणापेक्षा अधिक काही नसते.

काटेकोरपणे सांगायचे तर, सॅम्पलिंग ही स्वतंत्र मूल्यांची मालिका म्हणून सतत फंक्शनचे प्रतिनिधित्व करण्याची प्रक्रिया आहे आणि परिमाणीकरण म्हणजे सिग्नलचे (मूल्यांचे) स्तरांमध्ये विभाजन. कोडिंगसाठी, येथे कोडिंग हे कोडच्या पूर्वनिर्धारित संयोजनासह परिमाणीकरणाच्या परिणामी प्राप्त झालेल्या घटकांची तुलना म्हणून समजले जाते.

व्होल्टेजला कोडमध्ये रूपांतरित करण्याच्या अनेक पद्धती आहेत. याव्यतिरिक्त, प्रत्येक पद्धतीमध्ये वैयक्तिक वैशिष्ट्ये आहेत: अचूकता, वेग, जटिलता. रूपांतरण पद्धतीच्या प्रकारानुसार, ADC चे तीन वर्गीकरण केले जाते

-

समांतर

-

सुसंगत,

-

अनुक्रमांक-समांतर.

प्रत्येक पद्धतीसाठी, कालांतराने सिग्नलचे रूपांतर करण्याची प्रक्रिया स्वतःच्या मार्गाने पुढे जाते, म्हणून हे नाव. क्वांटायझेशन आणि एन्कोडिंग कसे केले जाते यात फरक आहेत: रूपांतरित सिग्नलवर डिजिटल परिणाम अंदाजे करण्यासाठी अनुक्रमांक, समांतर किंवा अनुक्रमांक-समांतर प्रक्रिया.

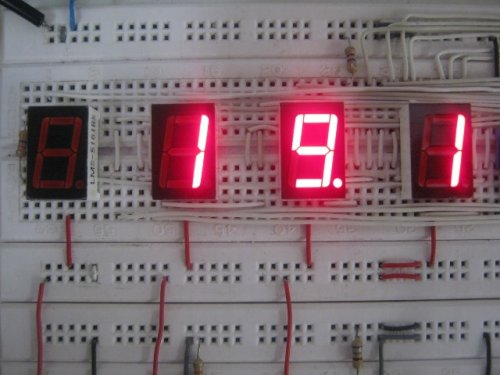

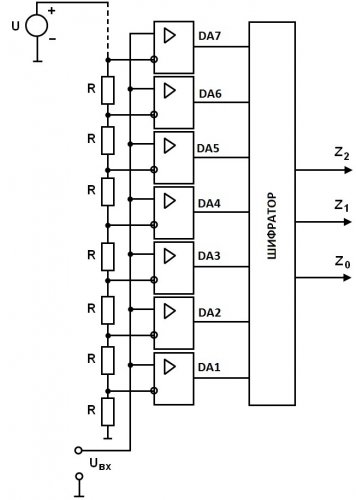

समांतर अॅनालॉग-टू-डिजिटल कन्व्हर्टरचा आकृती आकृतीमध्ये दर्शविला आहे. समांतर एडीसी हे सर्वात वेगवान अॅनालॉग-टू-डिजिटल कन्व्हर्टर आहेत.

इलेक्ट्रॉनिक तुलना उपकरणांची संख्या (डीए तुलनाकर्त्यांची एकूण संख्या) एडीसीच्या क्षमतेशी संबंधित आहे: तीन तुलनिक दोन बिटसाठी पुरेसे आहेत, तीनसाठी सात, चारसाठी 15 इ. रेझिस्टर व्होल्टेज विभाजक स्थिर संदर्भ व्होल्टेजची श्रेणी सेट करण्यासाठी डिझाइन केलेले आहे.

इनपुट व्होल्टेज (या इनपुट व्होल्टेजचे मूल्य येथे मोजले जाते) एकाच वेळी सर्व तुलनाकर्त्यांच्या इनपुटवर लागू केले जाते आणि हे प्रतिरोधक विभाजक मिळवू देत असलेल्या सर्व संदर्भ व्होल्टेजच्या तुलनेत.

ज्या तुलनाकर्त्यांचे नॉन-इनव्हर्टिंग इनपुट संदर्भापेक्षा जास्त व्होल्टेजसह दिले जातात (विभाजकाने इनव्हर्टिंग इनपुटवर लागू केले आहेत) ते आउटपुटवर एक तर्क देईल, बाकीचे (जेथे इनपुट व्होल्टेज संदर्भापेक्षा कमी किंवा समान आहे शून्य) शून्य देईल.

मग एक एन्कोडर कनेक्ट केला जातो, त्याचे कार्य म्हणजे एक आणि शून्याचे संयोजन मानक, पुरेशा समजल्या जाणार्या बायनरी कोडमध्ये रूपांतरित करणे.

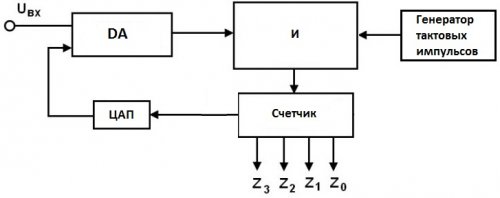

अनुक्रमांक रूपांतरणासाठी ADC सर्किट्स समांतर कन्व्हर्टर सर्किट्सपेक्षा कमी वेगवान आहेत, परंतु त्यांच्याकडे एक सोपी प्राथमिक रचना आहे. ते तुलनाकर्ता, आणि तर्कशास्त्र, एक घड्याळ, एक काउंटर आणि डिजिटल-टू-एनालॉग कनवर्टर वापरते.

आकृती अशा एडीसीचे आकृती दर्शवते. उदाहरणार्थ, तुलनात्मक सर्किटच्या इनपुटवर लागू केलेले मोजलेले व्होल्टेज दुसऱ्या इनपुट (संदर्भ) च्या रॅम्प सिग्नलपेक्षा जास्त असताना, काउंटर घड्याळ जनरेटरच्या नाडी मोजतो. असे दिसून आले की मोजलेले व्होल्टेज मोजलेल्या डाळींच्या संख्येच्या प्रमाणात आहे.

तेथे मालिका-समांतर एडीसी देखील आहेत, जेथे अॅनालॉग सिग्नलला डिजिटल सिग्नलमध्ये रूपांतरित करण्याची प्रक्रिया अंतराळात विभक्त केली जाते, म्हणून असे दिसून येते की कमीतकमी जटिलतेसह जास्तीत जास्त व्यापार-बंद गती प्राप्त केली जाते.